# **Advanced Formal Verification**

Edited by Rolf Drechsler

Kluwer Academic Publishers

# ADVANCED FORMAL VERIFICATION

# **Advanced Formal Verification**

Edited by

## **Rolf Drechsler**

University of Bremen, Germany

NEW YORK, BOSTON, DORDRECHT, LONDON, MOSCOW

eBook ISBN: 1-4020-2530-0 Print ISBN: 1-4020-7721-1

©2004 Kluwer Academic Publishers New York, Boston, Dordrecht, London, Moscow

Print ©2004 Kluwer Academic Publishers Dordrecht

All rights reserved

No part of this eBook may be reproduced or transmitted in any form or by any means, electronic, mechanical, recording, or otherwise, without written consent from the Publisher

Created in the United States of America

Visit Kluwer Online at: http://kluweronline.com

and Kluwer's eBookstore at: http://ebooks.kluweronline.com

# Contents

| Preface  |                    |                                                                      | xi            |

|----------|--------------------|----------------------------------------------------------------------|---------------|

| Contrib  | uting Au           | thors                                                                | xiii          |

| Introduc |                    |                                                                      | xix           |

| Rolf Dre | echsler            |                                                                      |               |

| 1        | Forma              | d Verification                                                       | xix           |

| 2        | Challe             | enges                                                                | xxi           |

| 3        | Contri             | ibutions to this Book                                                | xxiii         |

| 1        |                    |                                                                      |               |

| What Sa  | at-Solver          | rs can and cannot do                                                 | 1             |

| Eugene   | Goldberg           |                                                                      |               |

| 1        | Introd             | uction                                                               | 1             |

| 2        | Hard 1             | Equivalence Checking CNF formulas                                    | 3             |

|          | 2.1                | Introduction                                                         | $\frac{3}{5}$ |

|          | 2.2                | Common Specification of Boolean Circuits                             | 5             |

|          | 2.3                | Equivalence Checking as SAT                                          | 11            |

|          | 2.4                | Class $M(p)$ and general resolution                                  | 12            |

|          | 2.5                | Computation of existentially implied functions                       | 13            |

|          | 2.6                | Equivalence Checking in General Resolution                           | 14            |

|          | 2.7                | Equivalence Checking of Circuits with Unknown CS                     | 20            |

|          | 2.8                | A Procedure of Equivalence Checking for Circuits with                | 00            |

|          | 2.0                | a Known CS                                                           | 22            |

|          | $\frac{2.9}{2.10}$ | Experimental Results Conclusions                                     | 23<br>26      |

| 9        |                    |                                                                      |               |

| 3        | 3.1                | Sets of Points<br>Introduction                                       | 26<br>26      |

|          | $\frac{3.1}{3.2}$  | Stable Set of Points                                                 | 28            |

|          | $\frac{3.2}{3.3}$  | SSP as a reachable set of points                                     | 31            |

|          | 3.4                | Testing Satisfiability of CNF Formulas by SSP Con-                   | 91            |

|          | 0.1                | struction                                                            | 32            |

|          | 3.5                | Testing Satisfiability of Symmetric CNF Formulas by SSP Construction | 35            |

|          | 3.6                | SSPs with Excluded Directions                                        | 39            |

|          | 3.7                | Conclusions                                                          | 42            |

| A DVA NCED | FODMAI | VEDIEIC.      | $\Lambda TION$ |

|------------|--------|---------------|----------------|

| ADVANGED   | FORMAL | V E R I E I G | 4 / /(//V      |

| vi        | ADVANCED FORMAL VERIFICAT                                                                               | $\Gamma ION$    |

|-----------|---------------------------------------------------------------------------------------------------------|-----------------|

| 2         |                                                                                                         |                 |

| Advancer  | ments in mixed BDD and SAT techniques                                                                   | 45              |

| Gianpiero | o Cabodi and Stefano Quer                                                                               |                 |

| 1         | Introduction                                                                                            | 45              |

| 2         | Background                                                                                              | 47              |

|           | 2.1 SAT Solvers                                                                                         | 47              |

|           | 2.2 Binary Decision Diagrams                                                                            | 48              |

|           | 2.2.1 Zero-Suppressed Binary Decision Diagrams                                                          | 49              |

|           | <ul><li>2.2.2 Boolean Expression Diagrams</li><li>2.3 Model Checking and Equivalence Checking</li></ul> | $\frac{50}{52}$ |

| 3         |                                                                                                         | $\frac{52}{54}$ |

| 3         | Comparing SAT and BDD Approaches: Are they different?  3.1 Theoretical Considerations                   | 54              |

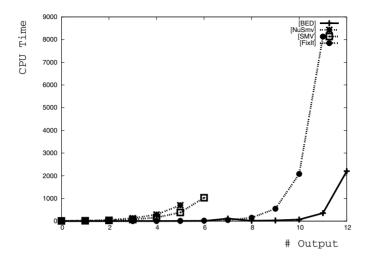

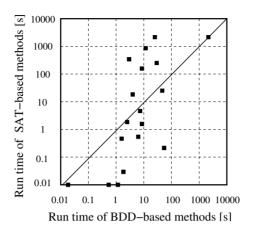

|           | 3.2 Experimental Benchmarking                                                                           | 55              |

|           | 3.2.1 Bug Hunting in an Industrial Setting                                                              | 56              |

|           | 3.2.2 Modifying BDD-based Techniques to Perform BMC                                                     | 56              |

|           | 3.2.3 Conclusions                                                                                       | 58              |

|           | 3.3 Working on Affinities: Variable Order                                                               | 58              |

|           | 3.3.1 Affinities on circuit-width correlation 3.3.2 Recursion tree and Variable Order                   | 59<br>59        |

|           | 3.3.2 Recursion tree and Variable Order 3.3.3 A Common Static Variable Order Heuristic                  | 60              |

|           | 3.3.4 Conclusions                                                                                       | 60              |

| 4         | Decision Diagrams as a Slave Engine in general SAT: Clause                                              | 00              |

| -         | Compression by Means of ZBDDs                                                                           | 61              |

|           | 4.1 ZBDDs for Symbolic Davis-Putnam Resolution                                                          | 61              |

|           | 4.2 ZBDDs for Symbolic DLL                                                                              | 62              |

|           | 4.3 ZBDDs for Breadth-First SAT                                                                         | 62              |

| _         | 4.4 Conclusions                                                                                         | 62              |

| 5         | Decision Diagram Preprocessing and Circuit-Based SAT<br>5.1 BED Preprocessing                           | 62<br>63        |

|           | 5.1 BED Preprocessing<br>5.2 Circuit-Based SAT                                                          | 64              |

|           | 5.2.1 BDD Sweeping and SAT                                                                              | 64              |

|           | 5.2.2 SAT on BEDs                                                                                       | 66              |

|           | 5.3 Preprocessing by Approximate Reachability                                                           | 67              |

| 6         | Using SAT in Symbolic Reachability Analysis                                                             | 68              |

|           | 6.0.1 BDDs at SAT leaves                                                                                | 69              |

|           | 6.0.2 SAT-Based Symbolic Image and Pre-image                                                            | 70              |

| 7         | Conclusions, Remarks and Future Works                                                                   | 71              |

| 3         |                                                                                                         |                 |

| Equivaler | nce Checking of Arithmetic Circuits                                                                     | 77              |

| Dominik   | Stoffel, Evgeny Karibaev, Irina Kufareva and Wolfgang Kunz                                              |                 |

| 1         | Introduction                                                                                            | 78              |

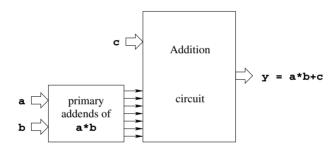

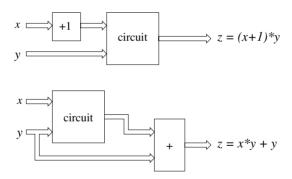

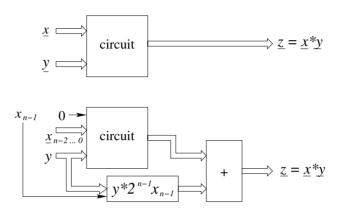

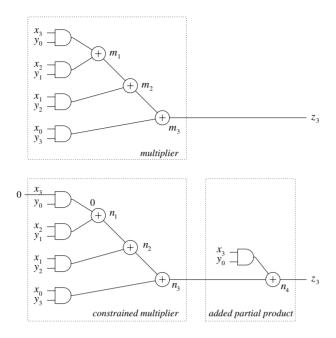

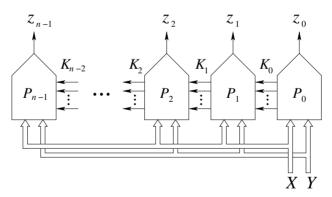

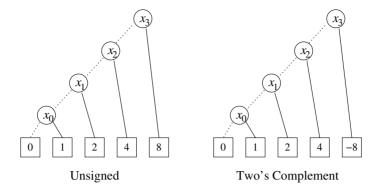

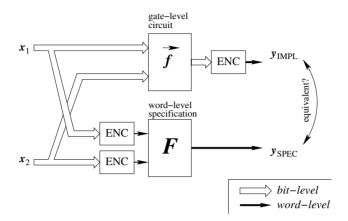

| 2         | Verification Using Functional Properties                                                                | 81              |

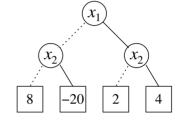

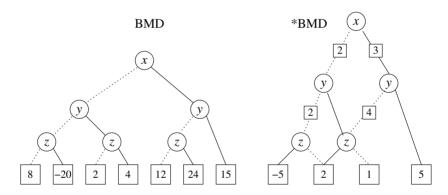

| 3         | Bit-Level Decision Diagrams                                                                             | 85              |

| 4         | Word-Level Decision Diagrams                                                                            | 88              |

| -         | 4.1 Pseudo-Boolean functions and decompositions                                                         | 89              |

|           | 4.2 *BMDs                                                                                               | 92              |

|           | 4.3 Equivalence Checking Using *BMDs                                                                    | 94              |

|           | 4.4 Experiments with *BMD synthesis                                                                     | 97              |

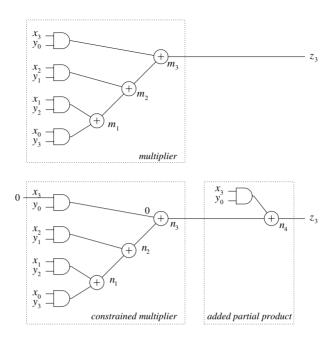

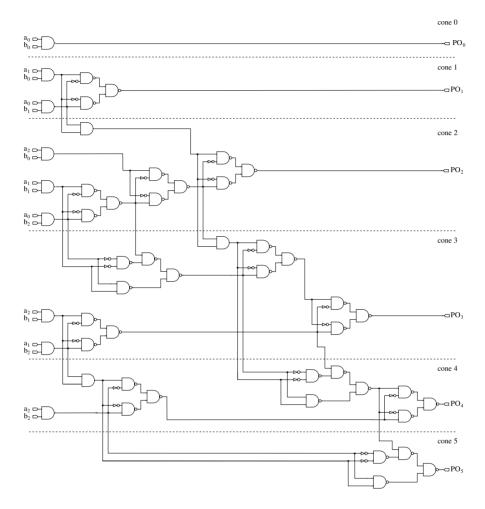

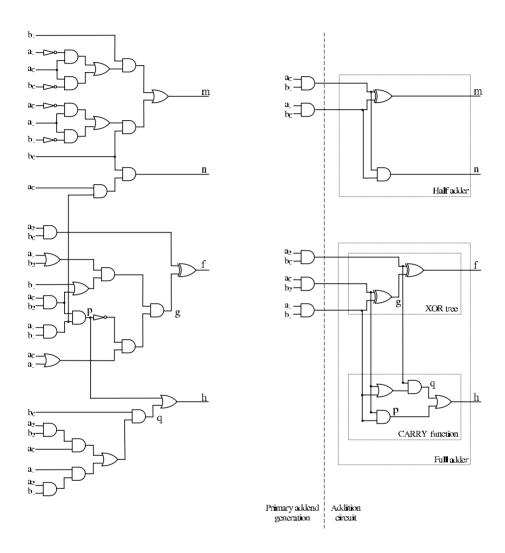

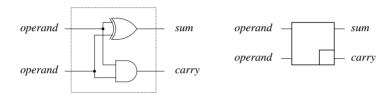

| 5         | Arithmetic Bit-Level Verification                                                                       | 105             |

|           | 5.1 Verification at the Arithmetic Bit Level                                                            | 108             |

|           | 5.2 Extracting the Half Adder Network                                                                   | 112             |

Contents vii

|           | 5.3               | Verification Framework                                               | 115               |

|-----------|-------------------|----------------------------------------------------------------------|-------------------|

|           | 5.4               | Experimental Results                                                 | 115               |

| 6         | Conclu            | sion                                                                 | 118               |

| 7         | Future            | Perspectives                                                         | 119               |

|           |                   |                                                                      |                   |

| ŧ<br>Appl | ication of Pr     | coperty Checking and Underlying Techniques                           | 125               |

|           |                   | Peer Johannsen and Klaus Winkelmann                                  |                   |

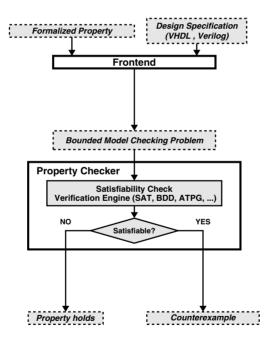

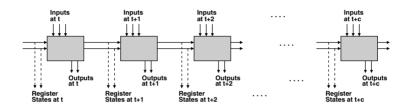

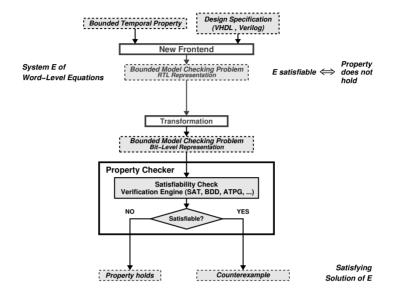

| 1         |                   | Verification Environment: User's View                                | 126               |

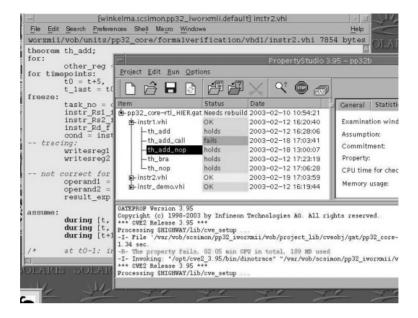

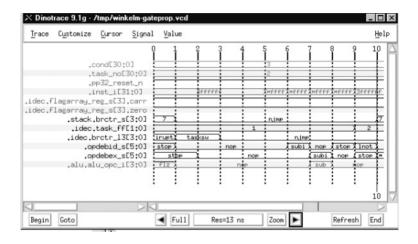

| -         | 1.1               | Tool Environment                                                     | 126               |

|           | 1.2               | The gateprop Property Checker                                        | 127               |

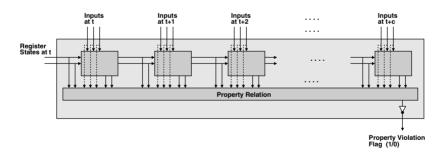

| 2         | Circuit           | Verification Environment: Underlying Techniques                      | 129               |

|           | 2.1               | From Property to Satisfiability                                      | 129               |

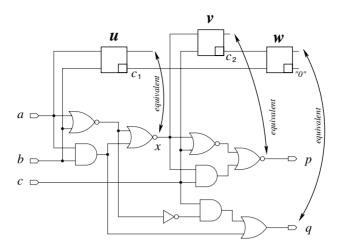

|           | 2.2               | Preserving Structure during Problem Construction                     | 131               |

|           | 2.3               | The Experimental Platform RtProp                                     | 132               |

| 3         | Exploit           | ting Symmetries                                                      | 133               |

|           | 3.1               | Symmetry in Property Checking Problems                               | 133               |

|           | 3.2               | Finding Symmetrical Value Vectors                                    | 136               |

|           | 3.3               | Practical Results                                                    | 140               |

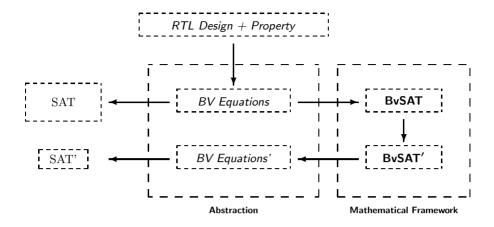

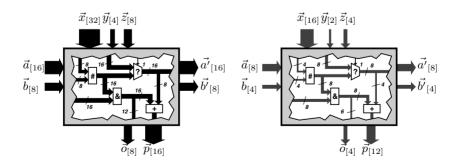

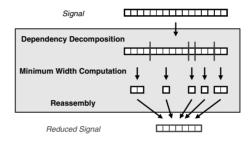

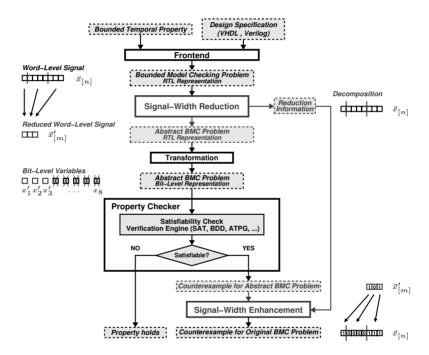

| 4         |                   | ated Data Path Scaling to Speed Up Property Checking                 | 142               |

|           | 4.1               | Bitvector Satisfiability Problems                                    | 143               |

|           | 4.2               | Formal Abstraction Techniques                                        | 145               |

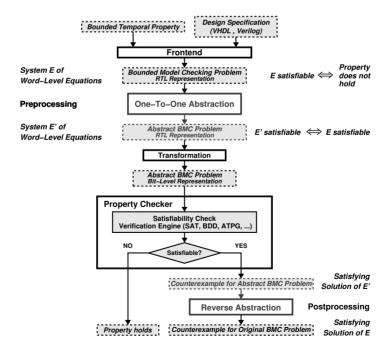

|           | 4.3               | Speeding Up Hardware Verification by One-To-One Abstraction          | 146               |

|           | 4.4               | Data Path Scaling of Circuit Designs                                 | $140 \\ 147$      |

| 5         |                   | ty Checking Use Cases                                                | 152               |

| 9         | 5.1               | Application Example: Reverse Engineering                             | 155               |

|           | 5.1.1             | Functionality                                                        | 155               |

|           | 5.1.2             | Task                                                                 | 155               |

|           | 5.1.3             | Examples for a property                                              | 156               |

|           | 5.1.4             | Results                                                              | 157               |

|           | 5.2               | Application Example: Complete Block-Level ASIC Ver-                  |                   |

|           | 501               | ification                                                            | 158               |

|           | 5.2.1             | Verification Challenge and Approach                                  | 158               |

|           | $5.2.2 \\ 5.2.3$  | Verifying the Control Path Data Path Results                         | $\frac{159}{160}$ |

|           | 5.2.4             | Overall Result                                                       | 160               |

|           | 5.3               | Productivity Statistics                                              | 161               |

| 6         | Summa             | · ·                                                                  | 162               |

| U         | 6.1               | Achievements                                                         | 162               |

|           | 6.2               | Challenges and Perspectives                                          | 163               |

|           |                   | •                                                                    |                   |

| )<br>^    |                   | V:                                                                   | 167               |

|           | rtion-Based       |                                                                      | 107               |

|           |                   | es Coelho Jr. and Harry D. Foster                                    | 40-               |

| 1         | Introdi           |                                                                      | 167               |

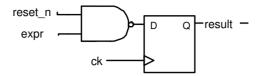

|           | 1.1               | Specifying properties  Observability and controllability             | $\frac{169}{171}$ |

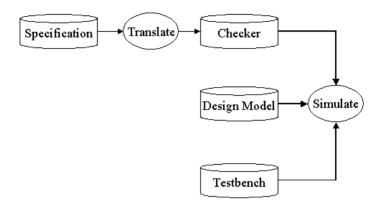

|           | $\frac{1.2}{1.3}$ | Observability and controllability Formal property checking framework | $\frac{171}{172}$ |

| 0         | _                 |                                                                      |                   |

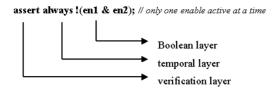

| 2         | Asserti<br>2.1    | on Specification Temporal logic                                      | $177 \\ 177$      |

|           | $\frac{2.1}{2.2}$ |                                                                      | 179               |

|           | 2.2               | Property Specification Language (PSL)                                | 119               |

|        |      | $2.2.1 \\ 2.2.2$    | Boolean layer<br>Temporal layer                            | 180<br>180        |

|--------|------|---------------------|------------------------------------------------------------|-------------------|

|        |      | 2.2.2               | Verification layer                                         | 182               |

|        | 3    |                     | ion libraries                                              | 183               |

|        | 4    |                     | ion simulation                                             | 184               |

|        | 5    |                     | ions and formal verification                               | 186               |

|        |      | 5.1                 | Handling complexity                                        | 186               |

|        |      | 5.2                 | Formal property checking role                              | 190               |

|        | 6    | Asserti             | ions and synthesis                                         | 191               |

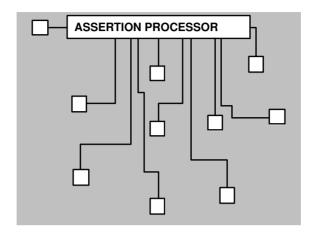

|        |      | 6.1                 | On-line validation                                         | 191               |

|        |      | 6.2                 | Synthesizable assertions                                   | 192               |

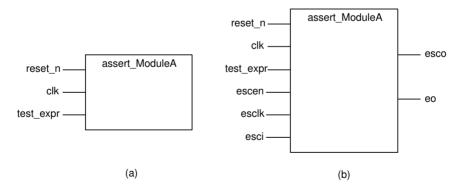

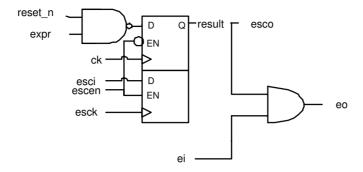

|        |      | $6.3 \\ 6.4$        | Routing scheme for assertion libraries                     | 194               |

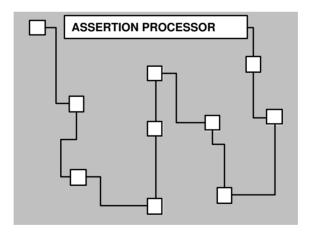

|        |      | 6.5                 | Assertion processors Impact of Assertions in Real Circuits | $\frac{195}{197}$ |

|        | 7    |                     | coperty specification example                              | 197               |

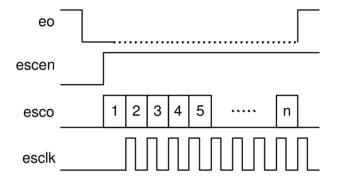

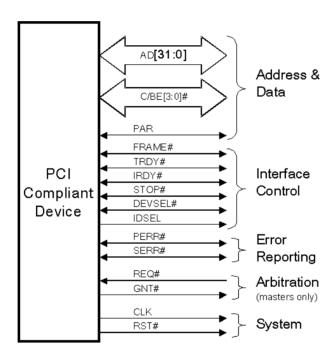

|        | 1    | 7.1                 | PCI overview                                               | 198               |

|        |      | 7.2                 | PCI master reset requirement                               | 199               |

|        |      | 7.3                 | PCI burst order encoding requirement                       | 199               |

|        |      | 7.4                 | PCI basic read transaction                                 | 200               |

|        | 8    | Summa               | ary                                                        | 202               |

| •      |      |                     |                                                            |                   |

| O<br>⊡ | 1 37 | :c:                 | f NI1: A1 Ct                                               | 205               |

|        |      |                     | on for Nonlinear Analog Systems                            | 200               |

| VV (   |      |                     | Ralf Klausen and Lars Hedrich                              | 200               |

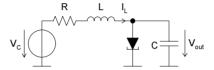

|        | 1    | Introd              |                                                            | 206               |

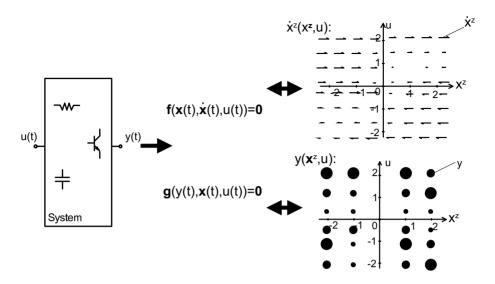

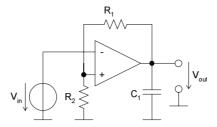

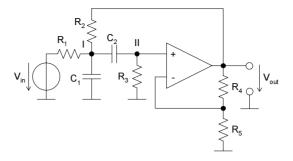

|        | 2    | System 2.1          | Description Apples Circuit Classes                         | $\frac{206}{208}$ |

|        |      | $\frac{2.1}{2.2}$   | Analog Circuit Classes<br>State Space Description          | $\frac{208}{208}$ |

|        |      | $\frac{2.2}{2.2.1}$ | Index                                                      | 209               |

|        |      | 2.2.2               | Solving a DAE System                                       | 209               |

|        |      | 2.2.3               | Linearized System Description                              | 211               |

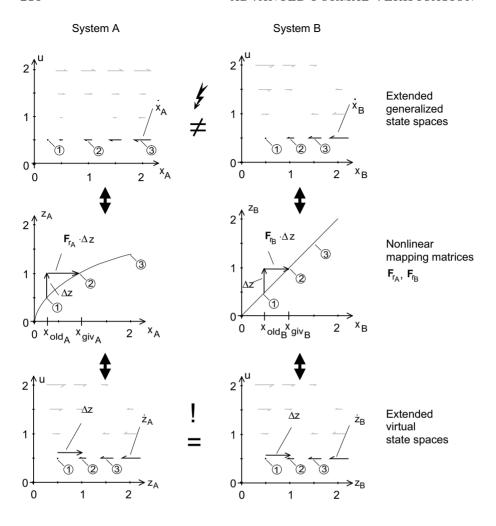

|        | 3    |                     | dence Checking                                             | 211               |

|        |      | 3.1                 | Basic Concepts                                             | 212               |

|        |      | 3.1.1               | Nonlinear Mapping of State Space Descriptions              | 212               |

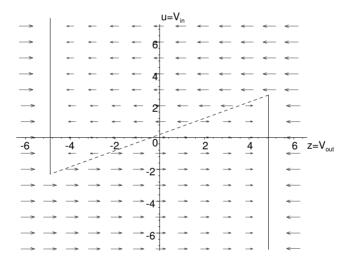

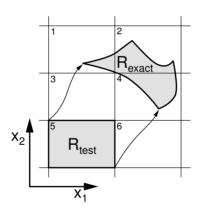

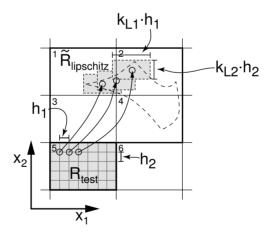

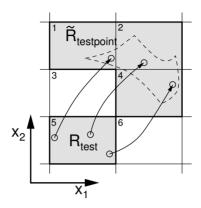

|        |      | $3.2 \\ 3.2.1$      | Equivalence Checking Algorithm Sampling the State Space    | 213<br>213        |

|        |      | 3.2.1 $3.2.2$       | Consistent Sample Point                                    | $\frac{215}{215}$ |

|        |      | 3.3                 | Linear Transformation Theory                               | $\frac{210}{217}$ |

|        |      | 3.3.1               | System Transformation to a Kronecker Canonical             |                   |

|        |      | 0.0.0               | Form                                                       | 217               |

|        |      | 3.3.2               | DAE System Transformation into the Virtual State Space     |                   |

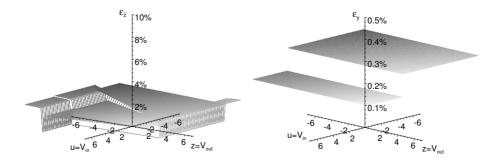

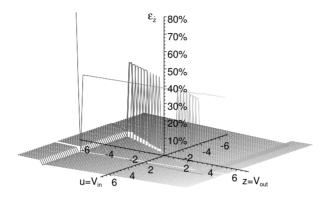

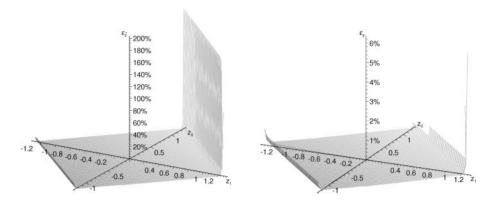

|        |      | 3.3.3<br>3.4        | Error Calculation Experimental Results                     | $\frac{222}{222}$ |

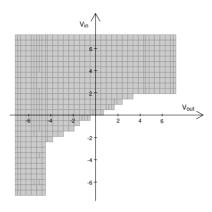

|        |      | 3.4.1               | Schmitt Trigger Example                                    | $\frac{222}{222}$ |

|        |      | 3.4.2               | Bandpass Example                                           | $\frac{1}{225}$   |

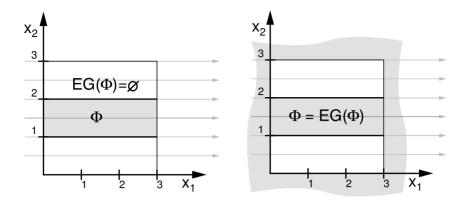

|        | 4    |                     | Checking                                                   | 227               |

|        |      | 4.1                 | Model Checking Language                                    | 227               |

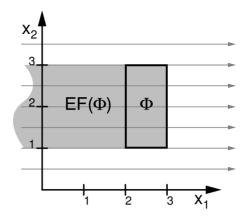

|        |      | 4.2                 | Analog Model Checking Algorithm                            | 230               |

|        |      | 4.2.1               | Transition Systems                                         | 230               |

|        |      | 4.2.2               | Discrete Time Steps                                        | 231               |

|        |      | 4.2.3 $4.2.4$       | State Space Subdivision<br>Transition Relation             | $\frac{232}{234}$ |

|        |      | 4.4.4               | TI AHSIMOH INCIAMOH                                        | 404               |

| C | ntents | X |

|---|--------|---|

| ~ |        | - |

|     |                                | 4.2.5 | Border Problems                 | 236 |

|-----|--------------------------------|-------|---------------------------------|-----|

|     |                                | 4.2.6 | Input Value Model               | 237 |

|     |                                | 4.2.7 | Optimizations                   | 239 |

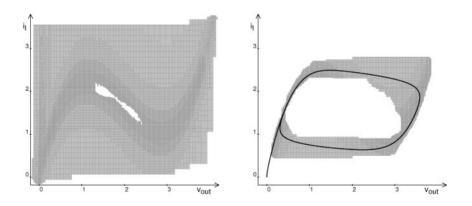

|     |                                | 4.3   | Experimental Results            | 239 |

|     |                                | 4.3.1 | Schmitt Trigger Example         | 239 |

|     |                                | 4.3.2 | Tunnel Diode Oscillator Example | 240 |

|     | 5                              | Sumn  | nary                            | 242 |

|     | 6                              | Ackno | owledgement                     | 242 |

|     | Appendix: Mathematical Symbols |       |                                 | 243 |

| Inc | dex                            |       |                                 | 247 |

#### **Preface**

Modern circuits may contain up to several hundred million transistors. In the meantime it has been observed that verification becomes the major bottleneck in design flows, i.e. up to 80% of the overall design costs are due to verification. This is one of the reasons why recently several methods have been proposed as alternatives to classical simulation. Simulation alone cannot guarantee sufficient coverage of the design resulting in bugs that may remain undetected.

As alternatives formal verification techniques have been proposed. Instead of simulating a design the correctness is proven by formal techniques. There are many different areas where these approaches can be used, like equivalence checking, property checking or symbolic simulation. Meanwhile these methods have been successfully applied in many industrial projects and have become the state-of-the-art technique in several fields. But the deployment of the existing tools in real-world projects also showed the weaknesses and problems of formal verification techniques. This gave motivating impulses for tool developers and researchers.

The book shows latest developments in the verification domain from the user and from the developer perspective. World leading experts describe the underlying methods of today's verification tools and describe various scenarios from industrial practice. In the first part of the book the core techniques of today's formal verification tools, like SAT and BDDs are addressed. In addition, instances known to be difficult, like multipliers, are studied. The second part gives insight in professional tools and the underlying methodology, like property checking and assertion based verification. Finally, to cope with complete system on chip designs also analog components have to be considered.

In this book the state-of-the-art in many important fields of formal verification is described. Besides the description of the most recent research results, open problems and challenging research areas are addressed. By this, the book is intended for CAD developers and researchers in the verification domain, where formal techniques become a

core technology to successful circuit and system design. Furthermore, the book is an excellent reference for users of verification tools to get a better understanding of the internal principles and by this to drive the tools to the highest performance. In this context the book is dedicated to all people in industry and academia to keep informed about the most recent developments in the field of formal verification.

#### Acknowledgment

All contributions in this edited volume have been anonymously reviewed. I would like to express my thanks for the valuable comments of the reviewers and their fast feedback, that allowed a timely publication. Here, I also like to thank all the authors who did a great job in submitting contributions of very high quality. My special thanks go to Görschwin Fey and Daniel Große from my group in Bremen in helping with the preparation of the book. Finally, I would like to thank Cindy Zitter and Mark DeJong from Kluwer Academic Publishers. All this would not have been possible without their steady support.

ROLF DRECHSLER

### **Contributing Authors**

Raik Brinkmann received his Masters Degree in Computer Science from Clausthal Technical University, in 1996. Before joining Infineon, he worked as verification engineer and embedded system designer at Siemens Information and Communication Networks. In 1999 he joined Siemens Corporate Technology to focus his research on formal methods for word-level verification, spending two years at the Infineon Design Center in San Jose, CA. He is also working towards his Ph.D. from University of Kaiserslautern. Currently, he is responsible for verification core technologies in the Infineon CVE formal verification team.

Gianpiero Cabodi received the MS degree in EECS in 1984 and the Ph.D. degree in 1989 from Politecnico di Torino. Since 1989 he has been with the Department of Automation and Computer Engineering of Politecnico di Torino, where he is currently an Associate Professor. He has worked within several EEC funded research projects, and he has been principal investigator of research contracts with DEC, COMPAQ and INTEL. His research interests cover a broad range, within the general framework of CAD for digital systems. He is well known for his scientific contributions within the field of Binary Decision Diagrams applied to Formal Verification. He is also interested in Boolean Satisfiability, Logic and High Level Synthesis, Testing, CAD applications in Parallel and Distributed environments.

Claudionor Nunes Coelho Jr. has a degree in Electrical Engineering (summa cum laude) and a Masters in Computer Science from the Federal University of Minas Gerais. He also holds a Ph.D. in Electrical Engineering and Computer Science from Stanford University. Claudionor was a member of the technical team of several start-up companies, working in an upper management position at Verplex Systems. He is a founder of several start-ups, including RDBIOTEC S.A. and i-Vision. He is also an advisor for FIR Capital Partners. He is currently a professor of Com-

puter Science at the Federal University of Minas Gerais. His interests include validation techniques for complex designs, embedded systems' design and software engineering.

Rolf Drechsler received his diploma and Dr. phil. nat. degree in computer science from the J.W. Goethe-University in Frankfurt am Main, Germany, in 1992 and 1995, respectively. He was with the Institute of Computer Science at the Albert-Ludwigs-University of Freiburg im Breisgau, Germany from 1995 to 2000. He joined the Corporate Technology Department of Siemens AG, Munich in 2000, where he worked as a Senior Engineer in the formal verification group. Since October 2001 he has been with the University of Bremen, Germany, where he is now a full professor for computer architecture. His research interests include verification, logic synthesis, and evolutionary algorithms.

Harry Foster serves as Chairman of the Accellera Formal Verification Technical Committee, which is currently defining the PSL property specification language standard. He is co-author of the Kluwer Academic Publishers book Assertion-Based Design, as well as the Kluwer book Principles of Verifiable RTL Design. Prior to joining Jasper Design Automation, Harry was Verplex Systems' Chief Architect. Harry has researched and developed formal verification tools and methodologies for over 12 years as a Senior Member of the CAD Technical Staff at Hewlett-Packard, and is the original co-creator of the Accellera Open Verification Library (OVL) assertion monitor standard.

Eugene Goldberg received his M.S. degree in theoretical physics from the Belorussian State University in 1983 and his Ph.D. degree in computer science from the Institute of Engineering Cybernetics of the Belorussian Academy of Sciences in 1995. From 1983 to 1995 he worked as a researcher in the laboratory of logic design at the Institute of Engineering Cybernetics. From 1996 to 1997 he was a visiting scholar at the University of California at Berkeley. He joined Cadence Berkeley Labs in November 1997. His main interests are development of efficient algorithms for computationally hard problems with emphasis on CAD applications.

Walter Hartong was born in Dinklage, Germany, on February 10, 1972. He graduated (Dipl.-Ing.) in electrical engineering at the University of Hannover in 1997. He was with the Institute of Microelec-

tronic Circuits and Systems of the University of Hannover since 1997, where he received his Ph.D. degree for his research on approaches to model checking for nonlinear analog systems in 2002. Since 2002 he is application engineer for analog/mixed signal circuit simulation at Cadence Design Systems, Munich, Germany. His research interests include: analog/mixed signal simulation, analog hardware description languages, behavioral modeling, symbolic analysis, and formal verification.

Lars Hedrich was born in Hannover, Germany, on February 19, 1966. He graduated (Dipl.-Ing.) in electrical engineering at the University of Hannover in 1992. Since 1992 he is with the Institute of Microelectronic Circuits and Systems at the Department of Computer Science of the University of Hannover, where he received his Ph.D. degree in electrical engineering for his research on approaches to formal verification of analog circuits in 1997. In 2002 he became a junior professor. His research interests include several areas of analog design automation: symbolic analysis of linear and nonlinear circuits, behavioral modeling, circuit synthesis, and formal verification.

Peer Johannsen received his Masters Degree in Computer Science at Christian-Albrechts-University of Kiel, Germany, in 1997. Afterwards he joined Siemens Corporate Research in Munich, focusing his work on formal techniques for hardware verification. He spent two years of research at the Infineon Design Center in San Jose, CA, working on new methods for property checking of digital circuits. In 2003 he received his Ph.D. in Computer Science from Christian-Albrechts-University of Kiel. Currently he is a project leader in the Infineon CVE formal verification team, responsible for the development of a new static verification tool.

Evgeny Karibaev received the B.S. and Dipl.-Ing. degrees in Electrical Engineering from the Department of Radio Physics at Tomsk State University, Tomsk, Russia, in 2000 and 2001, respectively. He is currently working toward his Ph.D. degree at the Dept. of Electrical and Computer Engineering at the University of Kaiserslautern. His research interests are in the field of formal hardware verification, including equivalence checking and property checking of arithmetic circuits.

Ralf Klausen was born in Hannover, Germany, on May 26, 1971. He graduated (Dipl.-Ing.) in electrical engineering at the University of Hannover in 2000. Since 2000 he is with the Institute of Microelectronic

Systems at the Department of Computer Science of the University of Hannover. He is working towards a Ph.D. degree on approaches to formal verification of analog circuits.

Irina Kufareva graduated from the department of Computer Science of Tomsk State University, Russia, with a Dipl.-Ing. degree in computer science in 1994. She received her Ph.D. in computer science in 2000. She currently works as an assistant professor at the Dept. of Radio Physics at Tomsk State University, Tomsk, Russia. Her current research interests include automata theory and formal verification.

Wolfgang Kunz obtained the Dipl.Ing. degree of electrical engineering from University of Karlsruhe in 1989 and the doctor's degree from University of Hannover in 1992. From 1989 to 1991 he was a graduate student at the ECE Department at the University of Massachusetts at Amherst. From 1993 to 1998 he was with Max Planck Fault-Tolerant Computing Group at the University of Potsdam. From 1998 to 2001 he was a professor at the CS department at the University of Frankfurt. Since 2001 he is with the EE department at the University of Kaiserslautern. Wolfgang Kunz conducts research in the areas of logic and layout synthesis, equivalence checking and ATPG. For his contributions in these areas he has received several awards including the IEEE Transactions on CAD Best Paper Award.

Stefano Quer received the MS degree in EECS in 1991 from Politecnico di Torino and the Ph. D. degree in 1996. In 1994, he was with the EECS Department of the University of California at Berkeley, in 1998, with the Advanced Technology Group, at Synopsys Inc., Mountain View, California, and in 1999, with the Alpha Development Group, at Compaq, Shrewsbury, Massachussetts. He has been consultant for Compaq Computer Corporation. He is currently Assistant Professor at Dipartimento di Automatica e Informatica of Politecnico di Torino. His research interests include hardware description languages, logic synthesis, formal verification, simulation and testing of digital circuits and systems.

**Dominik Stoffel** obtained his Diplom-Ingenieur degree from the University of Karlsruhe in 1992 and his Ph.D. from the University of Frankfurt in 1999. From 1994 to 1998 he was with the Max-Planck Fault-Tolerant Computing Group in Potsdam. From 1998 to 2001 he was with the Electronic Design Automation group at the University of Frankfurt,

Germany. Since 2001 he is working as a post-doctoral researcher in the Electronic Design Automation group at the University of Kaiserslautern. His research interests are in the field of logic synthesis and formal hardware verification

Klaus Winkelmann received a degree in Mathematics and, in 1984, his Ph.D. in computer science at Erlangen University. Currently he is a project manager in the Infineon CVE formal verification team, responsible for innovative applications of property checking technology. Before joining Infineon, he built up and led several R&D teams at Siemens Corporate Research, focusing on formal techniques for the design and verification of embedded software, in particular verification and synthesis of finite automata, synchronous languages, discrete event systems and their applications to industrial control. He also contributed to the application of AI techniques to problems of automation, control and diagnosis. He has acted as reviewer, project manager and as technical director for several European projects, and taught computer science courses in several universities.

### Introduction

Rolf Drechsler

With increasing design complexity, verification becomes a more and more important aspect of the design flow. Modern circuits contain up to several million transistors. In the meantime it has been observed that verification becomes the major bottleneck, i.e. up to 80% of the overall design costs are due to verification. This is one of the reasons why recently several methods have been proposed as alternatives to classical simulation, since it cannot guarantee sufficient coverage of the design. E.g. in [2] it has been reported that for the verification of the Pentium IV more than 200 billion cycles have been simulated, but this only corresponds to 2 CPU minutes, if the chip is run with 1 GHz.

Formal verification techniques have gained large attention, since they allow to prove the correctness of a circuit, i.e. they ensure 100% functional correctness. Besides being more reliable, formal verification approaches have also shown to be more cost effective in many cases, since test bench creation - usually a very time consuming and error prone task - becomes superfluous.

In this introduction, we first briefly describe some of the application domains, where formal techniques have successfully been used. We give some links to further literature where the interested reader can get more information. Then, a list of "challenging problems" is given, i.e. a list of topics that need further investigation in the context of formal hardware verification. Finally, the contributions to this book are briefly described.

#### 1. Formal Verification

The main idea of formal hardware verification is to prove the functional correctness of a design instead of simulating some vectors. For the proof process different techniques have been proposed. Most of them work in the Boolean domain, like  $Binary\ Decision\ Diagrams$  (BDDs) or SAT solvers.

The typical hardware verification scenarios where formal proof techniques are applied are

Equivalence Checking (EC) and

Property Checking (PC), also called Model Checking (MC).

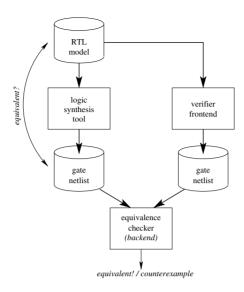

The goal of EC is to ensure the equivalence of two given circuit descriptions. These circuits might be given on different levels of abstraction, i.e. register transfer level or gate level. The main steps of an equivalence checker are as follows (see e.g. [12]):

- 1. Translate both designs to an internal format.

- 2. Establish the correspondence between the two designs in a matching phase.

- 3. Prove equivalence or inequivalence.

- 4. In case of an inequivalence a counter-example is generated and the debugging phase starts.

Notice that the circuit is considered as purely combinational by modeling the state elements as additional primary inputs and outputs. This modeling may result in counter-examples that are not reachable during normal circuit operation.

In contrast to EC, where two circuits are considered, for PC a single circuit is given and properties are formulated in a dedicated "verification language". It is then formally proven whether these properties hold under all circumstances. While "classical" CTL-based model checking [6] can only be applied to medium sized designs, approaches based on Bounded Model Checking (BMC) as discussed in [4] give very good results when used for complete blocks with up to 100k gates.

Nevertheless, all these approaches can run into problems caused by complexity, e.g. if the circuit becomes too large or if the function being represented turns out to be "difficult" for formal methods. The second problem often arises in cases of complex arithmetics, like multipliers.

Motivated by this, hybrid methods have been proposed, like e.g. symbolic simulation and assertion checking. These methods try to bridge the gap between simulation and correctness proofs. But these techniques also make use of formal proof techniques.

For more information on basics on formal verification techniques the reader is referred to [22].

*INTRODUCTION* xxi

#### 2. Challenges

Even though formal verification techniques are very successfully applied and have become the state-of-the-art in many design flows, still many problems exist. In this section a list of these problems is given. The list is not complete in the sense that all difficulties are covered, but many important ones are mentioned. This gives a better understanding of current problems in hardware verification, motivates for the following chapters of the book and shows directions for future research.

Complexity: According to Moore's law the complexity of the circuits steadily increases. For this, the underlying data structures are very important. For EC and BMC often dedicated data structures are used. For representation of the state space BDDs have shown to work well, but if the size of the circuit becomes too large the BDDs often suffer from "memory explosion".

Proof technology: While BDDs and SAT are the most popular techniques in hardware verification and have also been applied to many domains, there is still a lot of research going on (see also Chapter 1 and 2). Besides the classical monolithic approaches modern EC tools make use of multi-engine approaches that combine different techniques, like SAT, BDD, term rewriting, ATPG, and random pattern simulation. How to successfully combine these - often orthogonal - approaches is not fully understood today.

Word-level approaches: Even though most proof techniques today work on the bit-level, many studies have shown that significant improvements can be achieved if the proof engine makes use of high-level information or even completely works on a higher level of abstraction. In this context also ILP solvers showed promise (see also Chapter 4).

Matching in EC: As described above, before the proof process starts the correspondence between the circuits has to be established. Here, several techniques exist, like name-based, structural or proverbased, but still for large industrial designs these methods often fail. This results in very time consuming user defined matching.

Reachability of counter-examples: In EC and BMC the generated counter-example might not be reachable in normal circuit operation. This results from the modeling of the circuit, i.e. instead of a FSM only the combinational part is considered. Thus, it has to be checked that the counter-example is "valid" after it has been generated, or the prover has to ensure that it is reachable. Techniques

- have to be developed how this can be ensured without a complete reachability analysis of the FSM, that is usually not feasible due to complexity reasons.

- Arithmetic: Industrial practice has shown that today's proof techniques, like BDD and SAT, have difficulties with arithmetic circuits, like multipliers. Word-level approaches have been proposed as an alternative, but these methods turned out to often be difficult to integrate in fully automatic tools. For this, arithmetic circuits often occurring in circuit design are still difficult to handle (see Chapter 4).

- System integration: PC works best on the module level, i.e. for blocks with up to 100k gates. But in multi-chip modules many of these blocks are integrated to build a system. Due to complexity the modules cannot be verified as one large block and for this models and approaches are needed.

- Hybrid approaches: For complex blocks or on the system level PC might be a very complex task and for this simpler alternatives have been studied, i.e. techniques that are more powerful than classical simulation but need less resources than PC. Techniques, like symbolic simulation or assertion-based verification, in this context also make use of formal verification techniques (see also Chapter 5).

- Checker synthesis: The specified properties can also be synthesized and added to the design. In this way, they can also be used for on-line test after the circuit has been fabricated.

- Analog/mixed signal: Most EC and PC models assume that the circuit is purely digital, while in modern system-on-chip designs many analog components are integrated. For this, also models and proof mechanisms need to be developed for analog and mixed signal devices (see Chapter 6).

- Retiming: For EC retimed circuits are still difficult to handle, since in this case the state matching cannot be performed. Thus, the problem remains sequential and by this becomes far too complex.

- Multiple clocks: Many circuits have different clocking domains, while verification tools can often only work with a single clock.

- Coverage: To check the completeness of a verification process coverage metrics have to be defined. While typical methods, like state coverage, are much too weak in the context of formal verification,

*INTRODUCTION* xxiii

there still does not exist a good measure that is comfortable to use for PC.

Diagnosis: After a fault has been identified by a formal verification tool a counter-example is generated. The next step is to identify the fault location or a reason for the failing proof process. Here, also formal proof techniques can be applied.

Most solutions to these problems are still in a very early stage of development, but these fields have to be addressed to make formal hardware verification successful in industrial applications. To orient the reader, some recent references are provided to give a starting point for further studies: [25, 17, 22, 16, 9, 26, 13, 1, 7, 23, 21, 15, 5, 19, 24, 20, 11, 18, 27, 3, 14, 10, 8]

#### 3. Contributions to this Book

The book consists of six chapters that cover most of the aspects described above. Examples of proof technology are described and the latest developments in this field are presented. But also contributions from industrial practice show the importance of formal verification approaches in today's design flows. Each chapter provides experimental results and for each application domain open problems and directions for future work are outlined.

In Chapter 1, Eugene Goldberg analyses the core problem in formal techniques, i.e. the satisfiability problem. Resolution-based SAT solvers are analyzed and a new way of testing satisfiability is proposed.

Properties of SAT and BDDs are studied in Chapter 2 by Gianpiero Cabodi and Stefano Quer. Based on this analysis, the integration of the two currently most successful proof techniques is discussed.

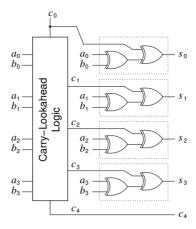

As mentioned above, formal proof techniques often have difficulties in handling arithmetic circuits. This issue is addressed in Chapter 3 by Dominik Stoffel, Evgeny Karibaev, Irina Kufareva and Wolfgang Kunz, where EC approaches are presented.

New innovative proof techniques that make use of word-level information are described by Raik Brinkmann, Peer Johannsen and Klaus Winkelmann, and an industrial property checking flow is presented in Chapter 4.

In Chapter 5, Claudionor Nunes Coelho Jr. and Harry D. Foster focus on assertion-based verification and in this context introduce a formal property language. The underlying methodology is introduced and implications for the user are addressed.

Finally, an approach to formal verification of analog circuits is proposed in Chapter 6 by Walter Hartong, Ralf Klausen and Lars Hedrich. MC and EC techniques for nonlinear analog systems are discussed.

#### References

- [1] L. Bening and H. Foster. *Principles of Verifiable RTL Design*. Kluwer Academic Publishers, 2001.

- [2] B. Bentley. Validating the Intel Pentium 4 microprocessor. In *Design Automation Conf.*, pages 244–248, 2001.

- [3] J. Bergeron. Writing Testbenches: Functional Verification of HDL Models. Kluwer Academic Publishers, 2003.

- [4] A. Biere, A. Cimatti, E.M. Clarke, M. Fujita, and Y. Zhu. Symbolic model checking using SAT procedures instead of BDDs. In *Design Automation Conf.*, pages 317–320, 1999.

- [5] R. Brinkmann and R. Drechsler. RTL-datapath verification using integer linear programming. In ASP Design Automation Conf., pages 741–746, 2002.

- [6] J.R. Burch, E.M. Clarke, K.L. McMillan, and D.L. Dill. Sequential circuit verification using symbolic model checking. In *Design Automation Conf.*, pages 46–51, 1990.

- [7] H. Chockler, O. Kupferman, R. Kurshan, and M. Vardi. A practical approach to coverage in model checking. In *Computer Aided Verification*, volume 2102 of *LNCS*, pages 66–77. Springer Verlag, 2001.

- [8] F. Copty, A. Irron, O. Weissberg, N. Kropp, and G. Kamhi. Efficient debugging in a formal verification environment. Software Tools for Technology Transfer, 4:335–348, 2003.

- [9] R. Drechsler. Formal Verification of Circuits. Kluwer Academic Publishers, 2000.

- [10] R. Drechsler. Synthesizing checkers for on-line verification of system-on-chip designs. In *Int'l Symp. Circ. and Systems*, pages IV:748–IV:751, 2003.

- [11] R. Drechsler and N. Drechsler. Evolutionary Algorithms for Embedded System Design. Kluwer Academic Publisher, 2002.

- [12] R. Drechsler and S. Höreth. Gatecomp: Equivalence checking of digital circuits in an industrial environment. In *Int'l Workshop on Boolean Problems*, pages 195–200, 2002.

- [13] R. Drechsler and D. Sieling. Binary decision diagrams in theory and practice. Software Tools for Technology Transfer, 3:112–136, 2001.

REFERENCES xxv

[14] H. Foster, A. Krolnik, and David J. Lacey. Assertion-Based Design. Kluwer Academic Publishers, 2003.

- [15] S. Hassoun and T. Sasao. *Logic Synthesis and Verification*. Kluwer Academic Publishers, 2001.

- [16] P.-H. Ho, T. Shiple, K. Harer, J. Kukula, R. Damiano, V. Bertacco, J. Taylor, and J. Long. Smart simulation using collaborative formal and simulation engines. In *Int'l Conf. on CAD*, pages 120–126, 2000.

- [17] Y. Hoskote, T. Kam, P. Ho, and X. Zhao. Coverage estimation for symbolic model checking. In *Design Automation Conf.*, pages 300–305, 1999.

- [18] Y.-C. Hsu, B. Tabbara, Y.-A. Chen, and F. Tsai. Advanced techniques for RTL debugging. In *Design Automation Conf.*, pages 362–367, 2003.

- [19] P. Johannsen and R. Drechsler. Formal verification on register transfer level utilizing high-level information for hardware verification. In *IFIP Int'l Conf. on VLSI*, pages 127–132, 2001.

- [20] R. Jones. Symbolic Simulation Methods for Industrial Formal Verification. Kluwer Academic Publishers, 2002.

- [21] A. Kölbl, J. Kukula, and R. Damiano. Symbolic RTL simulation. In *Design Automation Conf.*, pages 47–52, 2001.

- [22] Th. Kropf. Introduction to Formal Hardware Verification. Springer, 1999.

- [23] A. Kuehlmann, M. Ganai, and V. Paruthi. Circuit-based Boolean reasoning. In *Design Automation Conf.*, pages 232–237, 2001.

- [24] J. Mohnke, P. Molitor, and S. Malik. Limits of using signatures for permutation independent Boolean comparison. *Formal Methods in System Design: An International Journal*, 2(21):167–191, 2002.

- [25] D. Moundanos, J. Abraham, and Y. Hoskote. Abstraction techniques for validation coverage analysis and test generation. *IEEE Trans. on Comp.*, pages 2–14, January 1998.

- [26] P. Rashinkar, P. Paterson, and L. Singh. *System-on-a-Chip Verification*. Kluwer Academic Publishers, 2000.

- [27] A. Veneris, A. Smith, and M. S. Abadir. Logic verification based on diagnosis techniques. In ASP Design Automation Conf., 2003.

## Chapter 1

# WHAT SAT-SOLVERS CAN AND CANNOT DO

Eugene Goldberg

Cadence Berkeley Labs, USA

egold@cadence.com

#### Abstract

This chapter consists of two parts. In the first part we show that resolution based SAT-solvers cannot be scalable on real-life formulas unless some extra information about formula structure is known. In the second part we introduce a new way of satisfiability testing that may be used for designing more efficient and "intelligent" SAT-algorithms that will be able to take into account formula structure.

**Keywords:** Satisfiability problem, resolution, resolution proof complexity, equivalence checking, stable set of points, symmetric CNF formulas

#### 1. Introduction

In the last few years SAT-solvers have considerably improved their performance. As a result, the size of the CNF formulas that can be solved by state-of-the-art SAT-solvers [21, 23, 16, 8] in a reasonable time has dramatically increased. This success has lead to euphoria that reminds many people working in formal verification of early optimism caused by the appearance of BDDs [4]. However, enthusiasts forget that even though SAT-solvers can sometimes solve surprisingly large formulas, they are very far from being scalable (which is the same problem that made people less optimistic about BDDs).

In this chapter, we will try to give a more realistic estimation of the capabilities of SAT-solvers. The chapter is based on the results described in [10, 11, 12] and consists of two parts. The main point of the first part is that a SAT-solver cannot be scalable unless it is provided with some information about the structure of the CNF formula to be tested for satisfiability. In this part, we consider a class of formulas describ-

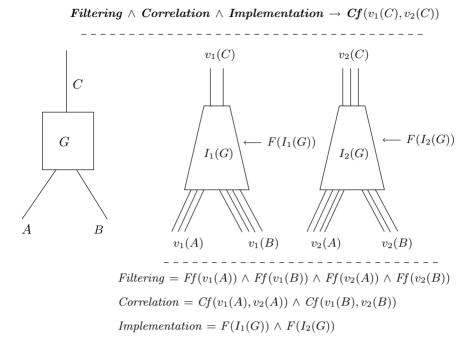

ing equivalence checking of combinational circuits that have a common specification (CS). A CS S of Boolean circuits  $N_1$  and  $N_2$  is just a circuit of multi-valued gates called blocks. Either Boolean circuit is obtained from S by replacing each block of S with its binary implementation. We show that there is a short resolution proof that  $N_1$  and  $N_2$  are equivalent however finding this proof by a deterministic algorithm is most likely infeasible unless a CS of  $N_1$  and  $N_2$  is known. On the one hand, it is bad news. This result means that SAT-algorithms cannot be scalable on equivalence checking CNF formulas (that are important from a practical point of view) even though they have short resolution proofs of unsatisfiability and so are very "easy". On the other hand, this is good news because one can have an efficient algorithm of equivalence checking if a CS of  $N_1$  and  $N_2$  is known. In other words, addressing the question implied by the title of this chapter one can say that SAT-solvers cannot be scalable if no information about high-level structure of formulas is provided.

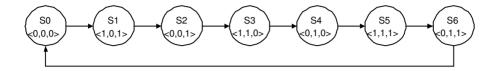

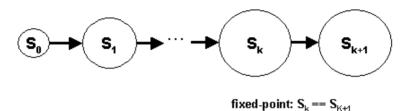

The result above implies that it is crucial for a SAT-solver to be able to take into account structural properties of formulas. The problem is that the existing SAT-solvers are based on the variable splitting paradigm introduced in the DPLL procedure [7]. During variable splitting a CNF formula is "mutilated" and its subtle structure is usually destroyed. In the second part of this chapter, we introduce a new procedure of satisfiability testing based on the notion of a stable set of points (SSP). It turns out that to prove that a CNF formula F is unsatisfiable it is sufficient to show that F evaluates to 0 (i.e. false) on a set of points called a stable set. In a sense, proving the unsatisfiability of a CNF formula by constructing its SSP can be viewed as "verification" by "simulation".

In general, SSPs are much smaller than the set of all possible assignments but the size of SSPs grows exponentially in the number of variables. So building a monolithic SSP point-by-point can not be used as the basis for designing efficient universal SAT-solvers. We describe two ways of using SSPs. First way is to compute an SSP modulo symmetries of the formula to be tested for satisfiability. In that case, even point-by-point computation of SSPs modulo symmetry can be efficient for highly symmetric formulas. Another way of using SSPs is to replace computing a monolithic SSP with constructing a sequence of much smaller SSPs of "limited" stability. Each such an SSP is stable if "movements" in some directions are forbidden.

#### 2. Hard Equivalence Checking CNF formulas

#### 2.1 Introduction

Since the general resolution system is the basis of almost all practical SAT-solvers, it has been the focus of attention for a long time. In the ground-breaking paper by Haken [13] it was shown that there is a class of CNF formulas for which only exponential size proofs are possible. (In the first part of this chapter we consider only unsatisfiable CNF formulas.) However, the impressive results of state-of-the-art SAT-solvers like Grasp, Sato, Chaff, BerkMin suggest that for the majority of CNF formulas one encounters in practice there should be short resolution proofs of their unsatisfiability. So a natural question to ask is whether the fact that a class of CNF formulas has short resolution proofs means that there is an algorithm that can find these short proofs or proofs that are "close" to them in length. (In complexity theory this question is posed as "whether the general resolution system is automatizable". Studying the automatizability of proof systems was started in [2]. In [18] some results on automatizability of general resolution were obtained.)

The objective of the first part of this chapter is to show that there is a class of CNF formulas that have very short resolution proofs in general resolution that are most likely very hard for a deterministic SAT-algorithm. These formulas specify equivalence checking of Boolean circuits and so they are very important from a practical point of view. This result means that the power of resolution based SAT-solvers is quite limited even for practical formulas that have provably short resolution proofs. The good news is that one can have an efficient SAT-algorithm for solving this class of formulas if some information about the structure of short proofs is provided.

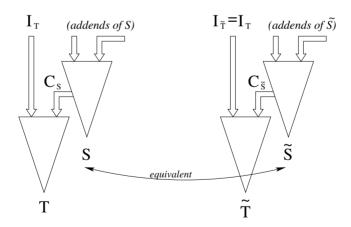

The class of formulas mentioned above describe equivalence checking of circuits having a common "specification". Let  $N_1$  and  $N_2$  be two functionally Boolean circuits with a common specification (CS) S. The CS S is just a circuit of multi-valued gates further referred to as blocks such that  $N_1$  (or  $N_2$ ) can be obtained from S by replacing each block G of S with its implementation  $I_1(G)$  (or  $I_2(G)$ ). The circuit  $I_1(G)$  (or  $I_2(G)$ ) implements the multi-output Boolean function obtained from the truth table of G after encoding the values of multi-valued variables with binary codes.

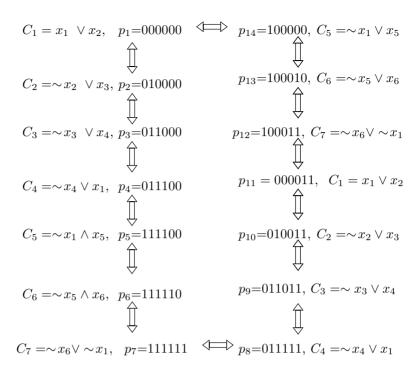

The problem of equivalence checking of  $N_1$  and  $N_2$  can be easily reduced to that of testing the unsatisfiability of a CNF formula (see Section 2.3). Let S consist of n blocks. Let F be a CNF specifying equivalence checking of  $N_1$  and  $N_2$ . We show that the unsatisfiability of F can be proven in general resolution in  $d * n * 3^{6p}$  resolution steps.

Here d is a constant and p is the size of the largest block G of the CS S (in terms of the number of gates one needs to implement G in  $N_1$  and  $N_2$ ). In particular, if p is bounded by a constant then we get a class of CNF formulas (in the paper it is denoted by M(p)) that has linear size resolution proofs. The parameter p is called the granularity of the specification S.

In spite of the fact that formulas from M(p) have short resolution proofs of unsatisfiability there are good reasons to believe that there does not exist an efficient SAT-algorithm for finding such proofs. Let F be a formula M(p) specifying equivalence checking of circuits  $N_1$  and  $N_2$  with a CS S. Let assume that the CS S is not known. On the one hand, the problem of finding S (or a good approximation of S) is most likely NP-hard. On the other hand, the short resolution proofs mentioned above are closely related to CSs of  $N_1$  and  $N_2$ . So given such a short proof of equivalence of  $N_1$  and  $N_2$  one could recover a "good" CS from this proof. Hence the existence of an efficient procedure for finding a short proof of equivalence would mean that there is an efficient algorithm for solving an NP-hard problem.

As we mentioned above the good news is that a formula F of M(p) can be efficiently solved by a deterministic algorithm if some extra information is provided. This extra information is a CS S of  $N_1$  and  $N_2$  whose equivalence checking the formula F specifies. (Namely, one just needs to know the assignment of gates of  $N_1$  and  $N_2$  to blocks of S. No other information about S is needed. In particular, one needs neither any knowledge of the functionality of blocks of S nor the knowledge of binary encodings used when producing  $N_1$  and  $N_2$  from S.) We formulate a specification aware algorithm of checking the unsatisfiability formulas from M(p) that has the same complexity as resolution proofs. That is it solves the formulas of M(p) in linear time.

The first part of this chapter is structured as follows. In Section 2.2 we introduce the notion of a CS of Boolean circuits that plays a key role in the following exposition. Section 2.3 describes a common way of reducing equivalence checking to SAT. In Section 2.4 we introduce a class M(p) of CNF formulas encoding equivalence checking of Boolean circuits with a CS of granularity p. We also describe the general resolution proof system. Section 2.5 describes computation of existentially implied functions that is used in Section 2.6. In the latter, we proof the main result of the first part of this chapter about the complexity of formulas from M(p) in general resolution. In Section 2.7 and 2.8 we discuss the complexity of formulas M(p) for deterministic resolution based algorithms. In Section 2.7 we give reasons why formulas from M(p) should be hard for deterministic SAT-algorithms that do not have any

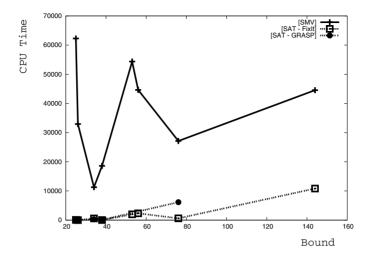

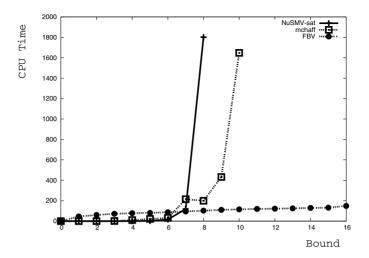

knowledge of a CS of the circuits checked for equivalence. In Section 2.8 we describe an efficient resolution based SAT-algorithm for equivalence checking of circuits with a known CS. In Section 2.9 we show experimentally that formulas from M(p) are hard for existing SAT-solvers while a specification aware algorithm easily solves them. In Section 2.10 some conclusions are made.

#### 2.2 Common Specification of Boolean Circuits

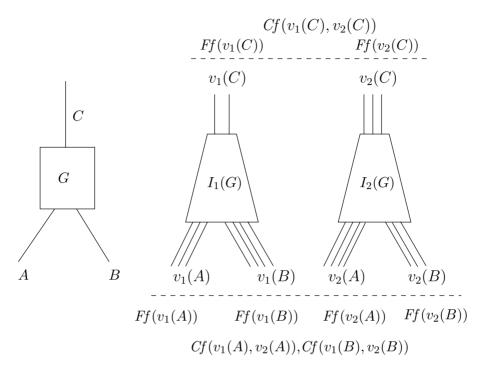

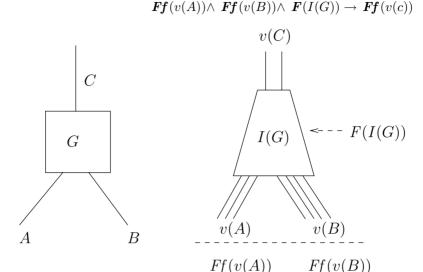

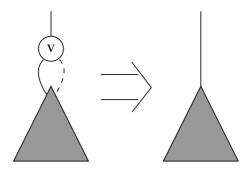

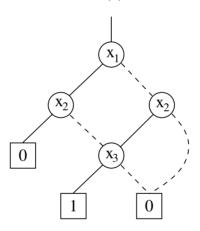

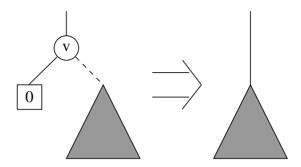

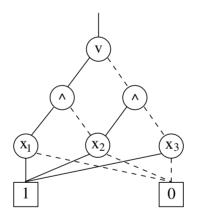

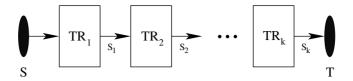

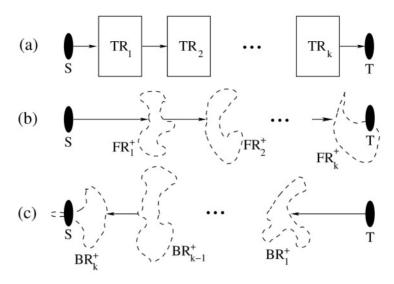

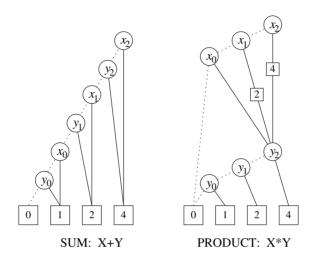

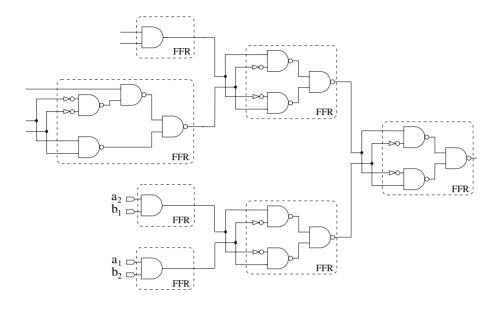

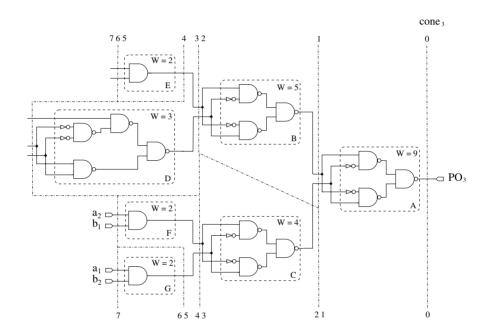

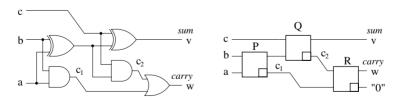

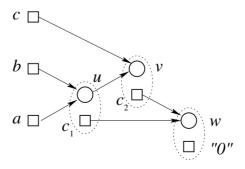

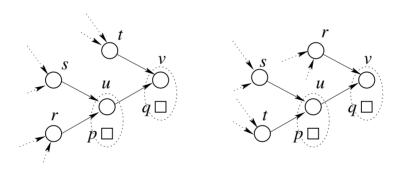

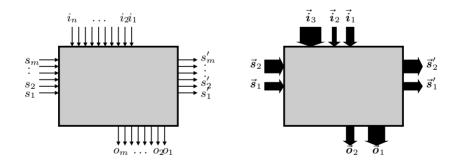

In this section, we introduce the notion of a common specification of Boolean circuits. Let S be a combinational circuit of multi-valued blocks (further referred to as a **specification**) specified by a directed acyclic graph H. (An example of specification is shown in Fig. 1.1a.) The sources and sinks of H correspond to primary inputs and outputs of S. Each non-source node of H corresponds to a multi-valued block computing a multi-valued function of multi-valued arguments. Each node n of H is associated with a multi-valued variable V. If n is a source of H, then the corresponding variable specifies values taken by the corresponding primary input of S. If n is a non-source node of S then the corresponding variable describes the values taken by the output of the block specified by n. If n is a source (respectively a sink), then the corresponding variable is called a primary input variable (respectively *primary output variable*). We will use the notation C=G(A,B) to indicate that a) the output of a block G is associated with a variable C; b) the function computed by the block G is G(A,B); c) only two nodes of H are connected to the node n in H and these nodes are associated with variables A and B.

Denote by D(A) the **domain** of a variable A associated with a node of H. The value of |D(A)| is called the **multiplicity** of A. If the multiplicity of every variable A of S is equal to 2 then S is a **Boolean** circuit.

Now we describe how a Boolean circuit N can be produced from a specification S by encoding the multi-valued variables. Let  $D(A) = \{a_1, \ldots, a_t\}$  be the domain of a variable A of S. Denote by q(A) **a Boolean encoding** of the values of D(A) that is a mapping  $q: D(A) \rightarrow \{0,1\}^m$ . Denote by length(q(A)) the number of bits in q that is the value of m. The value of  $q(a_i)$ ,  $a_i \in D(A)$  is called the **code** of  $a_i$ . Given an encoding q of length m of a variable A associated with a block of S, denote by v(A) the set of m **coding Boolean variables**.

**Example 1.1** Let B be a multi-valued variable and  $D(B) = \{b_1, b_2, b_3, b_4\}$ . Then the multiplicity of the variable B is 4. Let a mapping q be specified by the following expressions  $q(b_1) = 01, q(b_2) = 01$

$11, q(b_3) = 10, q(b_4) = 00$ . Then q specifies an encoding of the values of B of length(q(B)) equal to 2. The set of coding variables  $v(B) = \{q_1, q_2\}$  consists of two Boolean variables. The Boolean vector 01 where  $q_0 = 0, q_1 = 1$  is the code of  $b_1$  under the encoding q.

In the following exposition we make the assumptions below.

**Assumption 1.1** Each gate of a Boolean circuit and each block of a specification has two inputs and one output.

**Assumption 1.2** The multiplicity of each primary input (or output) variable of a specification is a power of 2.

**Assumption 1.3** If V is a primary input (or output) variable of a specification, then  $length(q(A)) = log_2(|D(A)|)$

**Assumption 1.4** If  $a_1$  and  $a_2$  are values of a variable A of a specification and  $a_1 \neq a_2$ , then  $q(a_1) \neq q(a_2)$ .

**Assumption 1.5** If A and B are two different variables of a specification, then  $v(A) \cap v(B) = \emptyset$ .

**Remark 1.1** From Assumptions 1.2, 1.3 and 1.4 it follows that if A is a primary input (or output) variable, a mapping  $q: D(A) \to \{0,1\}^m$  is bijective. In particular, any assignment to the variables of v(A) is a code of some value  $a \in D(A)$ .

**Definition 1.1** Given a Boolean circuit I, denote by Inp(I) (respectively Out(I)) the set of variables associated with primary inputs (respectively primary outputs) of I.

**Definition 1.2** Let  $X_1$  and  $X_2$  be sets of Boolean variables and  $X_2 \subseteq X_1$ . Let y be an assignment to the variables of  $X_1$ . Denote by  $proj(y, X_2)$  the **projection** of y on  $X_2$  i.e. the part of y that consists of the assignments to the variables of  $X_2$ .

**Example 1.2** Let  $X_1 = \{x_1, x_2, x_3, x_4, x_5\}$  and  $X_2 = \{x_1, x_3, x_5\}$  that is  $X_2 \subseteq X_1$ . Let y be the assignment  $(x_1 = 0, x_2 = 1, x_3 = 1, x_4 = 0, x_5 = 0)$  to the variables of  $X_1$ . Then  $proj(y, X_2)$  is equal to  $(x_1 = 0, x_3 = 1, x_5 = 0)$ .

**Definition 1.3** Let C = G(A,B) be a block of specification S. Let q(A), q(B), q(C) be encodings of variables A,B, and C respectively. A Boolean

circuit I is said to **implement the block** G if the following three conditions hold:

- The set Inp(I) is a subset of  $v(A) \cup v(B)$ .

- The set Out(I) is equal to v(C).

- If the set of values assigned to v(A) and v(B) form codes q(a) and q(b) respectively where  $a \in D(A)$ ,  $b \in D(B)$ , then I(z')=q(c) where z' is the projection of the assignment z=(q(a),q(b)) on Inp(I), I(z') is the value taken by I at z', and c=G(a,b)

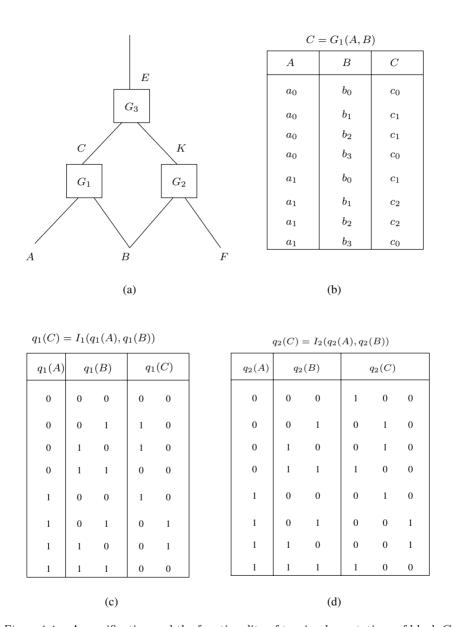

**Example 1.3** In Fig. 1.1a a specification of three blocks is shown. The functionality of two different implementations of the block  $C=G_1(A,B)$  (Fig 1.1b) is shown in Fig. 1.1c and 1.1d. Here  $D(A)=\{a_0,a_1\}$ ,  $D(B)=\{b_0,b_1,b_2,b_3\}$  and  $D(C)=\{c_0,c_1,c_2\}$ . Since A and B are primary input variables they are encoded with a minimum length code and  $q_1(A)=q_2(A)$  and  $q_1(B)=q_2(B)$  where  $q_1(a_0)=0$ ,  $q_1(a_1)=1$ ,  $q_1(b_0)=00$ ,  $q_1(b_1)=01$ ,  $q_1(b_2)=10$ ,  $q_1(b_3)=11$ . Finally, the encodings  $q_1(C)$  and  $q_2(C)$  are  $q_1(c_0)=00$ ,  $q_1(c_1)=10$ ,  $q_1(c_2)=01$  and  $q_2(c_0)=100$ ,  $q_2(c_1)=010$ ,  $q_2(c_2)=001$ .

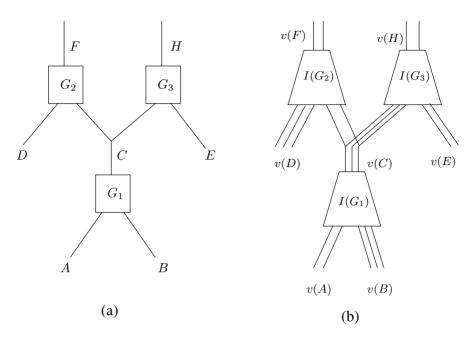

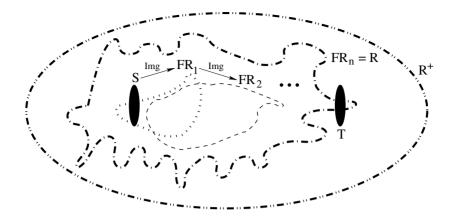

Remark 1.2 The reason why Inp(I) in Definition 1.3 may not include all the variables of v(A) and/or v(B) is that the function G(A,B) may not distinguish some values of A or B. (G(A,B) does not distinguish, say, values  $a_1, a_2 \in D(A)$ , if for any  $b \in D(B)$ ,  $G(a_1,b) = G(a_2,b)$ .) So to implement G(A,B) the circuit I may need only a subset of variables of  $v(A) \cup v(B)$ . This situation is illustrated in Fig. 1.2. Due to the fact that some values of the variable C are indistinguishable by  $G_2$ , only two outputs of the implementation block  $I(G_1)$  (out of the three) are connected to the inputs of  $I(G_2)$ . This said, henceforth, for the sake of simplicity, we will write I(q(a),q(b)) meaning I(q'(a),q'(b)), q'(a)=proj(q(a),Inp(I)) and q'(b)=proj(q(b),Inp(I)).

**Definition 1.4** Let S be a multi-valued circuit. A Boolean circuit N is said to **implement the specification** S, if it is built according to the following two rules.

- lacksquare Each block G of S is replaced with an implementation I of G.

- Let the output of block  $G_1$  (specified by variable C) be connected to an input of block  $G_2$  (specified by the same variable C) in S. Then the outputs of the circuit  $I_1$  implementing  $G_1$  are properly

Figure 1.1. A specification and the functionality of two implementations of block  $G_1$

Figure 1.2. A specification and its implementation

connected to inputs of circuit  $I_2$  implementing  $G_2$ . Namely, the primary output of  $I_1$  specified by a Boolean variable  $q_i \in v(C)$  is connected to the input of  $I_2$  specified by the same variable of v(C) if  $q_i \in Inp(I_2)$ .

Fig. 1.2 gives an example of a specification (Fig. 1.2a) and its implementation (Fig. 1.2b).

**Remark 1.3** Let N be an implementation of a specification S. Let p be the largest number of gates used in an implementation of a multi-valued block of S in N. We will say that S is a specification of **granularity** p for N.

**Definition 1.5** The topological level of a block G in a specification S is the length of the longest path from a primary input of S to G. (The length of a path is measured in the number of blocks on it. The topological level of a primary input is assumed to be 0.) Denote by level(G) the topological level of G in S.

**Remark 1.4** Let N be an implementation of a specification S. From Remark 1.1 it follows that for any value assignment h to the input variables of N there is a unique set of values  $(x_1, \ldots, x_k)$ , where  $x_i \in D(X_i)$

such that  $h=(q(x_1),\ldots,q(x_k))$ . That is there is one-to-one correspondence between assignments to primary inputs of S and N. The same applies to primary outputs of S and N.

**Definition 1.6** Let N be an implementation of S. Given a Boolean vector y of assignments to the primary inputs of N, the corresponding vector  $Y = (x_1,...,x_k)$  such that  $y = (q(x_1),...,q(x_k))$  is called the **pre-image** of y.

**Proposition 1.1** Let N be a circuit implementing specification S. Let I(G) be the implementation of a block C=G(A,B) of S in N. Let y be a value assignment to the primary input variables of N and Y be the pre-image of y. Then the values taken by the primary outputs of I(G) (under the assignment y to the inputs of N) form the code q(c) of a value  $c, c \in D(C)$ . The latter is the value taken by the output of G when the inputs of S take the values specified by Y.

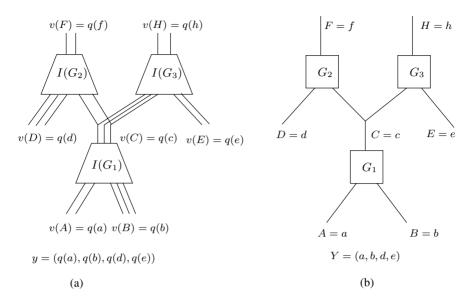

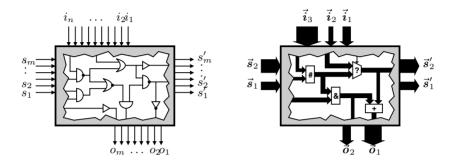

Proofs of Proposition 1.1 and the following Proposition 1.2 are simple and so we omit them. Instead, we explain Proposition 1.1 in Fig. 1.3. Suppose that y is an assignment to the primary input variables of the Boolean circuit (Fig. 1.3a) that is an implementation of the specification shown in Fig. 1.3b. According to Remark 1.4, y can be represented as (q(a), q(b), q(d), q(e)) where a, b, d, e are values of the variables A, B, D, E of the specification respectively. The pre-image of y is the vector Y = (a, b, d, e). Then the outputs of gates  $G_1, G_2$  and  $G_3$  take values  $c = G_1(a, b), f = G_2(d, c)$  and  $h = G_3(c, e)$  respectively. Since  $I(G_1), I(G_2)$  and  $I(G_3)$  are implementations of  $G_1, G_2, G_3$  respectively, their outputs take values q(c), q(f) and q(h) respectively.

**Proposition 1.2** Let  $N_1$ ,  $N_2$  be circuits implementing a specification S. Let each primary input (or output) variable X of S have the same encoding in  $N_1$  and  $N_2$ . Then Boolean circuits  $N_1$  and  $N_2$  are functionally equivalent.

**Definition 1.7** Let  $N_1$ ,  $N_2$  be two functionally equivalent Boolean circuits. Let  $N_1$ ,  $N_2$  implement a specification S so that for every primary input (output) variable X encodings  $q_1(X)$  and  $q_2(X)$  (used when producing  $N_1$  and  $N_2$  respectively) are identical. Then S is called **a common specification** (CS) of  $N_1$  and  $N_2$ .

**Assumption 1.6** Let S be a CS of  $N_1,N_2$  and C be a variable of S. We will assume that  $v_1(C) = v_2(C)$  if C is a primary input variable and  $v_1(C) \cap v_2(C) = \emptyset$  otherwise.

Figure 1.3. An illustration to Proposition 1.1

**Definition 1.8** Let S be a CS of  $N_1, N_2$ . Let  $p_1$  (respectively  $p_2$ ) be the granularity of S with respect to  $N_1$  (respectively  $N_2$ ). Then we will say that S is a CS of  $N_1, N_2$  of granularity  $p = max(p_1, p_2)$ .

**Definition 1.9** Given two functionally equivalent Boolean circuits  $N_1$ ,  $N_2$ , S is called the **finest common specification** if it has the smallest granularity p among all the CSs of  $N_1$  and  $N_2$ .

### 2.3 Equivalence Checking as SAT

In this section, we recall a common way of reducing equivalence checking to the satisfiability problem.

**Definition 1.10** A disjunction of literals of Boolean variables not containing two literals of the same variable is called a **clause**. A conjunction of clauses is called a **conjunctive normal form** (CNF).

**Definition 1.11** Given a CNF F, the satisfiability problem (SAT) is to find a value assignment to the variables of F for which F evaluates to 1 (also called a satisfying assignment) or to prove that such an assignment does not exist. A clause K of F is said to be satisfied by a value assignment y if K(y) = 1. If K(y) = 0, the clause K is said to be falsified by y.

The standard conversion of an equivalence checking problem into an instance of SAT is performed in two steps. Let  $N_1$  and  $N_2$  be Boolean circuits to be checked for equivalence. At the first step of this conversion, a circuit M called a miter [3] is formed from  $N_1$  and  $N_2$ . The miter M is obtained by 1) identifying the corresponding primary inputs of  $N_1$  and  $N_2$ ; 2) XORing each pair of corresponding primary outputs of  $N_1$  and  $N_2$ ; 3) ORing the outputs of the added XOR gates. So the miter of  $N_1$  and  $N_2$  evaluates to 1 if and only if for some input assignment a primary output of  $N_1$  and the corresponding output of  $N_2$  evaluate to different values. Therefore, the problem of checking the equivalence of  $N_1$  and  $N_2$  is equivalent to testing the satisfiability of the miter of  $N_1$  and  $N_2$ .

At the second step of conversion, the satisfiability of the miter is reduced to that of a CNF formula F. This formula is a conjunction of CNF formulas  $F_1,...,F_n$  specifying the functionality of the gates of M and a one-literal clause that is satisfied only if the output of M is set to 1. The CNF  $F_i$  specifies the i-th gate  $g_i$  of M. Any assignment to the variables of  $F_i$  that is inconsistent with the functionality of  $g_i$  falsifies a clause of  $F_i$  (and vice versa, a consistent assignment satisfies all the clauses of  $F_i$ .) For instance, the AND gate  $y=x_1x_2$  is specified by the following three clauses  $\sim x_1 \lor \sim x_2 \lor y$ ,  $x_1 \lor \sim y$ ,  $x_2 \lor \sim y$ .

### 2.4 Class M(p) and general resolution

In this short section we formally define the class of equivalence checking formulas we consider in the first part of this chapter. Besides, we describe the general resolution system.

**Definition 1.12** Given a constant p, a CNF formula F is a member of the class M(p) if and only if it satisfies the following two conditions.